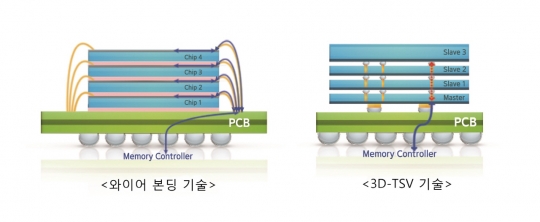

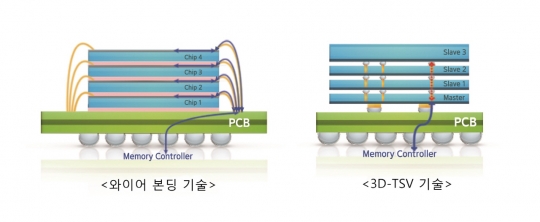

삼성전자가 새로 개발한 3D-TSV(왼쪽)와 종전에 쓰던 와이어본딩 패키지 기술 비교 사진. /삼성전자

삼성전자가 패키징 기술에서도 '초격차'를 증명해냈다. 더 작고 빠른 PC를 만들 수 있게 되면서 메모리 반도체 수요 증가에도 기여할 수 있을 것으로 기대된다.

삼성전자는 최근 '12단 3D-TSV(3차원 실리콘 관통전극)' 기술 개발에 성공했다고 7일 밝혔다. 세계 최초다.

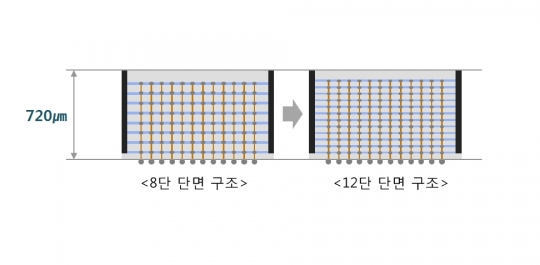

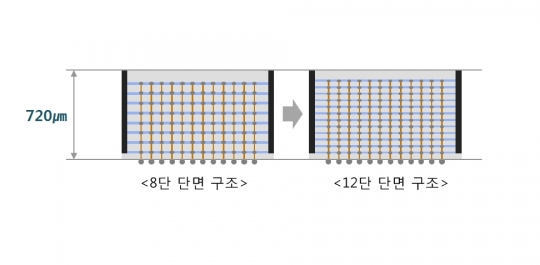

삼성전자는 이 기술을 이용해 업계 표준인 고대역폭 메모리(HBM)2와 동일한 두께(720㎛)로도 50% 이상 용량을 높이면서도 빠르고 소비전력을 줄일 수 있는 차세대 고용량 제품을 만들어낼 수 있게 됐다.

최신 제품인 16Gb D램칩을 사용하면 업계 최대 용량인 24GB 고대역폭 메모리(HBM) 제품도 구현할 수 있을 전망이다. 현재 주력제품인 8단 8GB 제품보다도 3배나 많은 용량이다.

삼성전자는 고객수요에 따라 새 기술을 적용한 제품을 적기에 공급해 프리미엄 반도체 시장 선도를 이어간다는 계획이다.

반도체 패키징은 생산된 반도체를 상품화하는 사업이다. 단순히 칩 형태인 반도체 여러개를 기판 등과 함께 묶어 PC와 서버 등에 장착할 수 있도록 만들어낸다.

삼성전자는 반도체칩 상단과 하단에 전자 이동 통로(TSV) 6만개를 만들어 서로를 오차없이 연결하는 기술을 개발하는데 성공했다. 종전에는 금선으로 칩을 연결해 적지않은 면적을 할당해야했지만, 머리카락 굵기 20분의 1수준 TSV를 사용해 공간 효율을 극대화했다.

3D-TSV 기술을 사용한 기존 표준 규격을 지키면서도 용량을 50% 더 늘릴 수 있다. 기존 8단 구조(왼쪽)와 새로운 12단 구조 비교. / 삼성전자

이 기술은 면적을 줄이는 것뿐 아니라, 전송 속도도 높였다. 종전 방법보다 전송 거리가 짧아 신호를 주고받는 시간을 줄일 수 있기 때문이다. 아울러 소비전력도 획기적으로 개선할 수 있게 됐다.

삼성전자는 100나노미터인 종이 두께보다 절반 이하로 가공한 D램칩 12개를 적층하고 수직으로 연결해 새로운 기술 개발에 성공했다. 반도체 패키징 업계에서도 가장 어려운 기술로 평가받는다.

삼성전자가 새로운 패키징 기술을 개발하면서 서버 업계에서도 새로운 수요를 만들어낼 것으로 예상된다. 최근 클라우드 서비스가 빠르게 확대되면서 더 작은 서버를 구축하려는 움직임이 이어지고 있다. 딥러닝 사용도 늘어나면서 더 빠른 메모리 필요성도 꾸준히 대두돼왔다.

삼성전자 DS부문 TSP총괄 백홍주 부사장은 "인공지능, 자율주행, HPC(고성능 컴퓨팅) 등 다양한 응용처에서 고성능을 구현할 수 있는 최첨단 패키징 기술이 날로 중요해지고 있다"며 "기술의 한계를 극복한 혁신적인 '12단 3D-TSV 기술'로 반도체 패키징 분야에서도 초격차 기술 리더십을 이어가겠다"고 말했다.

Copyright ⓒ 메트로신문 & metroseoul.co.kr

Copyright ⓒ 메트로신문 & metroseoul.co.kr